This set of VLSI Multiple Choice Questions & Answers (MCQs) focuses on “Noise Margin”.

1. Noise Margin is:

a) Amount of noise the logic circuit can withstand

b) Difference between VOH and VIH

c) Difference between VIL and VOL

d) All of the Mentioned

View Answer

Explanation: Noise Margin is defined as the amount of noise the logic circuit can withstand, it is given by the difference between VOH and VIH or VIL and VOL.

2. The VIL is found from transfer characteristic of inverter by:

a) The point where the straight line at VOH ends

b) The slope of the transition at a point at which the slope is equal to -1

c) The midpoint of the transition line

d) All of the mentioned

View Answer

Explanation: The VIL is the input voltage at which the slope of the transition will be equal to -1.

3. The VIH is found from transfer characteristic of inverter by:

a) The point where straight line at VOH ends

b) The slope of the transition at a point at which the slope is equal to -1

c) The midpoint of the transition line

d) All of the mentioned

View Answer

Explanation: The VIH is the input voltage at which the slope of the transition will be equal to -1. In Transfer characteristics at 2 points we will find the slope to be -1.

4. The relation between threshold voltage and Noise Margin is:

a) Vth = sqrt(Noise Margin)

b) Vth = NMH – NML

c) Vth = (NMH+NML)/2

d) None of the metioned

View Answer

Explanation: None.

5. The Lower Noise Margin is given by:

a) VOL – VIL

b) VIL – VOL

c) VIL ~ VOL(Difference between VIL and VOL, depends on which one is greater)

d) All of the Mentioned

View Answer

Explanation: Noise margin = VIL-VOL.

6. The Higher Noise Margin is given by:

a) VOH – VIH

b) VIH – VOH

c) VIH ~ VOH(Difference between VIH and VOH, depends on which one is greater)

d) All of the mentioned

View Answer

Explanation: Noise margin = VOH – VIH.

7. The Uncertain or transition region is between:

a) VIH and VOH

b) VIL and VOL

c) VIH and VIL

d) VOH and VOL

View Answer

Explanation: In Input the uncertain region is VIH and VIL.

8. The noise immunity ____________ with noise margin.

a) Decreases

b) Increases

c) Constant

d) None of the Mentioned

View Answer

Explanation: The noise immunity is directly proportional to noise margin.

9. If VIL of the 2nd gate is higher than VOL of the 1st gate, then logic output 0 from the 1st gate is considered as:

a) Logic input 1

b) Uncertain

c) Logic input 0

d) None of the mentioned

View Answer

Explanation: Logic output 0 from first gate is considered as logic input 0 at second gate as it lies within the range.

10. If VIL of the 2nd gate is lower than VOL of the 1st gate, then logic output 0 from the 1st gate is considered as:

a) Logic input 1

b) Uncertain

c) Logic input 0

d) None of the mentioned

View Answer

Explanation: The level of output signal from 1st gate is higher than the range for low input at 2nd gate. So it is uncertain.

11. Input Voltage between VIL and VOL is considered as:

a) Logic Input 1

b) Logic Input 0

c) Uncertain

d) None of the mentioned

View Answer

Explanation: None.

12. If VIH of the 2nd gate is higher than VOH of the 1st gate, then logic output 0 from the 1st gate is considered as:

a) Logic input 1

b) Uncertain

c) Logic input 0

d) None of the mentioned

View Answer

Explanation: The level of output signal from 1st gate is higher than the range for low input at 2nd gate. So it is uncertain.

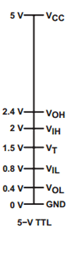

13. Determine the Noise Margin for 5V TTL inverter gate:

a) NMH = 0.4V and NML =0.4V

b) NMH = 2.4V and NML = 0.4V

c) NMH = 2V and NML = 0.8V

d) NMH = 1.5V and NML = 0.4V

View Answer

Explanation: None.

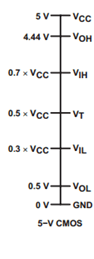

14. Determine the Noise Margin for 5V CMOS inverter gate:

a) NMH = 1V and NML = 1V

b) NMH = 3.7V and NML = 0.2V

c) NMH = 0.9V and NML = 1V

d) NMH = 0.2V and NML = 0.5V

View Answer

Explanation: None.

15. Noise margin of CMOS is:

a) Better than TTL and ECL

b) Less than TTL and ECL

c) Equal to TTL and ECL

d) None of the Mentioned

View Answer

Explanation: None.

Sanfoundry Global Education & Learning Series – VLSI.

To practice all areas of VLSI, here is complete set of 1000+ Multiple Choice Questions and Answers.

If you find a mistake in question / option / answer, kindly take a screenshot and email to [email protected]