This set of VLSI Multiple Choice Questions & Answers (MCQs) focuses on “Phase Lock Loop”.

1. The PLL device is:

a) Feedback system that compares output frequency and input frequency

b) Feedback system that compares output phase and input phase

c) Linear system that compares output resistance and input resistance

d) Non Linear system that compares output current and input current

View Answer

Explanation: The PLL device is a feedback system that compares output phase and input phase.

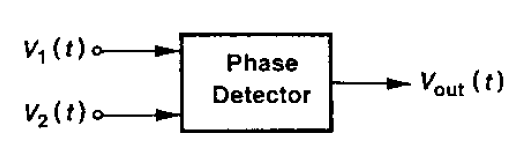

2. The Logic gate that works similar to phase detector is:

a) AND gate

b) OR gate

c) XOR gate

d) NOT gate

View Answer

Explanation: 2 input XOR gate works similar to Phase detector.

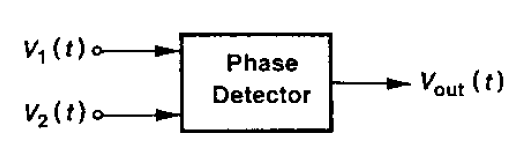

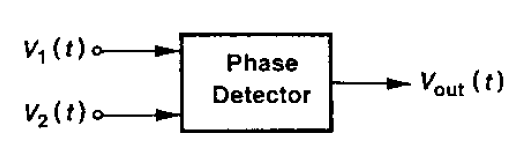

3. What is the input at the phase detector?

a) V1(t) – V2(t)

b) Phase(V1) + Phase(V2)

c) Phase(V1) – Phase(V2)

d) V1(t) + V2(t)

View Answer

Explanation: None.

4. What is the relation between input and output in the following circuit?

a) Exponential

b) Linear

c) Sinusoidal

d) None of the mentioned

View Answer

Explanation: None.

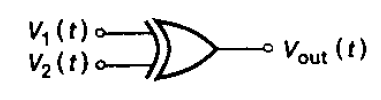

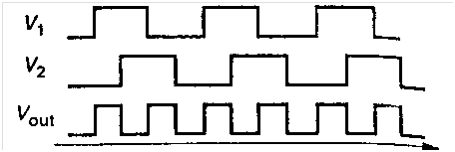

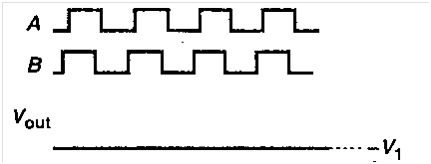

5. The correct input output waveform when the phase difference between 2 input voltages is 90 degrees

a)

b)

c)

d)

View Answer

Explanation: None.

6. The aligning of output phase of voltage controlled oscillator with reference is called:

a) Phase compensation

b) Phase alignment

c) Phase Locking

d) Phase detecting

View Answer

Explanation: The aligning of output phase of voltage controlled oscillator with reference is called Phase Locking.

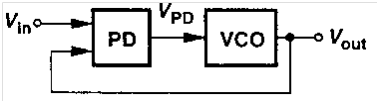

7. The block diagram of basic PLL consists of:

a)

b)

c)

d) None of the Mentioned

View Answer

Explanation: None.

8. What is the function of LPF in the following block diagram?

a) Suppress high frequency components of VCO output and presenting low frequency AC signal to PD

b) Suppress high frequency components of PD output and presenting low frequency AC signal to VCO

c) Suppress high frequency components of PD output and presenting DC signal to VCO

d) None of the mentioned

View Answer

Explanation: The function of LPF in PLL is to suppress high frequency components of PD output and presenting DC signal to VCO.

9. Instead of Phase detection, if Frequency detector is used the drawback PLL would face is:

a) Finite difference between input and output frequency

b) Equality cannot be established if PLL compared input and output frequency rather than pulses

c) Error between Vin and Vout cannot be removed

d) All of the mentioned

View Answer

Explanation: None.

10. If the input of type 1 PLL is a frequency step of Δw at t = 0, the change in phase at t = infinity is:

a) Δw

b) Δw/Kpd

c) Δw/Kpd.Kvco

d) None of the mentioned

View Answer

Explanation: None.

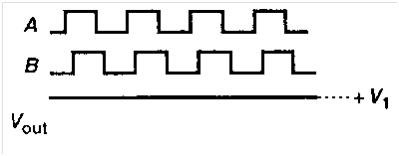

11. The correct input-output waveforms of Frequency detector:

a)

b)

c)

d)

View Answer

Explanation: None.

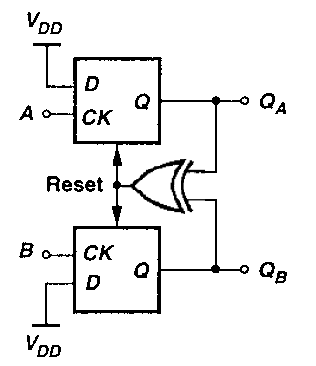

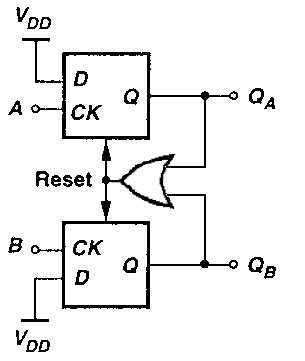

12. The D Flip Flop implementation for PFD is:

a)

b)

c)

d) None of the mentioned

View Answer

Explanation: None.

13. If high pass filter is used instead of Low pass filter in the PLL the response of PLL would be:

a) Output Voltage is not a square wave

b) Output Voltage contains many high frequency waves

c) VCO will be unstable due to variations in control voltage

d) All of the mentioned

View Answer

Explanation: None.

14. Number of poles in Type 1 PLL is:

a) 0

b) 1

c) 2

d) None of the mentioned

View Answer

Explanation: None.

15. The transfer function of PD is :

a) Constant

b) Varies with frequency

c) Varies with voltage

d) None of the Mentioned

View Answer

Explanation: None.

Sanfoundry Global Education & Learning Series – VLSI.

To practice all areas of VLSI, here is complete set of 1000+ Multiple Choice Questions and Answers.

If you find a mistake in question / option / answer, kindly take a screenshot and email to [email protected]