This set of Linear Integrated Circuit Multiple Choice Questions & Answers (MCQs) focuses on “Monolithic Phase-Locked Loop”.

1. What is the conversion ratio of the phase detector in 565 PLL?

a) 0.14

b) 0.35

c) 0.4458

d) 0.7

View Answer

Explanation: The conversion ratio of the phase detector of 565 PLL (Monolithic PLL) Kφ = 1.4/π = 0.4458.

2. Given fo = 1.2kHz and V = 13v, find the lock-in range of monolithic Phase-Locked Loop.

a) ±575Hz

b) ±720Hz

c) ±150Hz

d) ±1kHz

View Answer

Explanation: The lock-in range of monolithic PLL, △fL = ±(7.8×fo)/V = ±(7.8×1.2kHz)/13 = ±720Hz.

3. Find out the incorrect statement.

Monolithic phase detector is preferred for critical applications as it is:

1. Independent of variation in amplitude

2. Independent of variation in duty cycle of the input waveform

3. Independent of variation in response time

a) 1 & 2

b) 1 & 3

c) 2 & 3

d) 1, 2 & 3

View Answer

Explanation: Monolithic phase detectors are not sensitive to harmonics of the input signal and change in duty cycle of input and output frequency.

4. Determine the capture range of IC PLL 565 for a lock-in range of ± 1kHz.

a) △fc = ±31.453Hz

b) △fc = ±66.505Hz

c) △fc = ±87.653Hz

d) None of the mentioned

View Answer

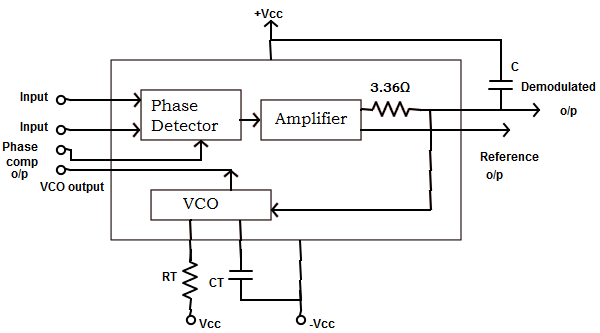

Explanation: The capture range is △fc = ±[△fL/ (2π×3.6×103×C]0.5 = ±[1kHz/(2π×3.6×kΩ×10µF)]0.5 = ±[1kHz/226.08×-6]0.5 = [4423]0.5 = ±66.505Hz.

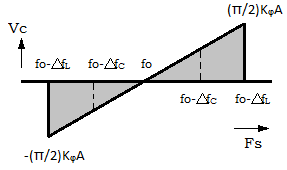

5. Find the lock-in range of monolithic Phase-Locked Loop from the given diagram.

a) -fo-△fL to fo-△fL

b) -fo-△fL to -fo-△fC

c) fo-△fL to fo-△fC

d) -fo-△fC to fo-△fC

View Answer

Explanation: Lock-in range of monolithic PLL is from -fo-△fL to fo-△fL.

6. At what range the PLL can maintain the lock in the circuit?

a) Lock in range

b) Input range

c) Feedback loop range

d) None of the mentioned

View Answer

Explanation: The change in frequency of the incoming signal can be tracked when the PLL is locked. So, the range of frequencies over which PLL maintains the lock with the incoming signal is called as the lock in range.

7. At which state the phase-locked loop tracks any change in input frequency?

a) Free running state

b) Capture state

c) Phase locked state

d) All of the mentioned

View Answer

Explanation: In the phase-locked, the output frequency is exactly same as the input signal frequency. So the circuit tracks any change in the input frequency through its repetitive action.

Sanfoundry Global Education & Learning Series – Linear Integrated Circuits.

To practice all areas of Linear Integrated Circuits, here is complete set of 1000+ Multiple Choice Questions and Answers.

If you find a mistake in question / option / answer, kindly take a screenshot and email to [email protected]