This set of VLSI Multiple Choice Questions & Answers (MCQs) focuses on “CMOS Logics”.

1. In Pseudo-nMOS logic, n transistor operates in

a) cut off region

b) saturation region

c) resistive region

d) non saturation region

View Answer

Explanation: In Pseudo-nMOS logic, n transistor operates in a saturation region and p transistor operates in resistive region.

2. The power dissipation in Pseudo-nMOS is reduced to about ________ compared to nMOS device.

a) 50%

b) 30%

c) 60%

d) 70%

View Answer

Explanation: The power dissipation in Pseudo-nMOS is reduced to about 60% compared to nMOS device.

3. Pseudo-nMOS has higher pull-up resistance than nMOS device.

a) true

b) false

View Answer

Explanation: Pseudo-nMOS has higher pull-up resistance than nMOS device and thus inverter pair delay is larger.

4. In dynamic CMOS logic _____ is used.

a) two phase clock

b) three phase clock

c) one phase clock

d) four phase clock

View Answer

Explanation: In dynamic CMOS logic, four phase clock is used in which actual signals are used to derive the clocks.

5. In clocked CMOS logic, output in evaluated in

a) on period

b) off period

c) both periods

d) half of on period

View Answer

Explanation: In clocked CMOS logic, the logic is evaluated only in the on period of the clock. And owing to the extra transistor in series, slower rise time and fall times are expected.

6. In clocked CMOS logic, rise time and fall time are

a) faster

b) slower

c) faster first and then slows down

d) slower first and then speeds up

View Answer

Explanation: In clocked CMOS logic, rise time and fall time are slower because of more number of transistors in series.

7. In CMOS domino logic _____ is used.

a) two phase clock

b) three phase clock

c) one phase clock

d) four phase clock

View Answer

Explanation: In CMOS domino logic, single phase clock is used. Clock signals distributed on one wire is called as single or one phase clock.

8. CMOS domino logic is same as ______ with inverter at the output line.

a) clocked CMOS logic

b) dynamic CMOS logic

c) gate logic

d) switch logic

View Answer

Explanation: CMOS domino logic is same as that of the dynamic CMOS logic with inverter at the output line.

9. CMOS domino logic occupies

a) smaller area

b) larger area

c) smaller & larger area

d) none of the mentioned

View Answer

Explanation: CMOS domino logic structure occupies smaller area than conventional CMOS logic as only n-block is used.

10. CMOS domino logic has

a) smaller parasitic capacitance

b) larger parasitic capacitance

c) low operating speed

d) very large parasitic capacitance

View Answer

Explanation: CMOS domino logic has smaller parasitic capacitance and higher operating speed.

11. In CMOS domino logic _______ is possible.

a) inverting structure

b) non inverting structure

c) inverting and non inverting structure

d) very complex design

View Answer

Explanation: In CMOS domino logic, only non inverting structures are possible because of the presence of the inverting buffer.

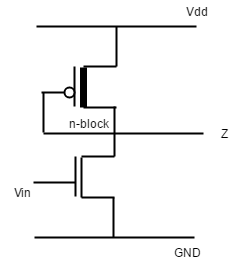

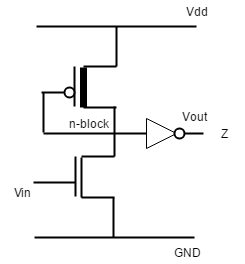

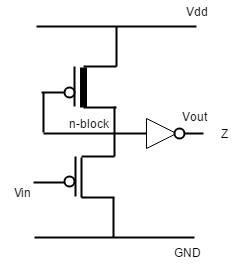

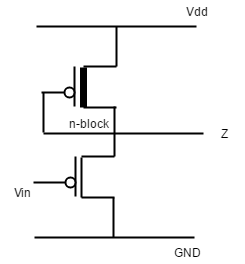

12. CMOS domino logic can be expressed diagramatically as

a)

b)

c)

d)

View Answer

Explanation: The correct form of CMOS domino logic representation is as given in the answer.

Sanfoundry Global Education & Learning Series – VLSI.

To practice all areas of VLSI, here is complete set of 1000+ Multiple Choice Questions and Answers.

If you find a mistake in question / option / answer, kindly take a screenshot and email to [email protected]