This set of Logic Design Multiple Choice Questions & Answers (MCQs) focuses on “S-R Flip-Flop, J-K Flip-Flop, D and T Flip-Flop”.

1. S-R Flip-Flop does not suffer from race conditions.

a) True

b) False

View Answer

Explanation: The input combination S = R = 1 is not allowed as it causes the same race conditions that occur in the S-R Latch. The race condition in hardware is when the behavior of the circuit becomes unpredictable.

2. The J-K Flip-Flop does not suffer from a Race condition.

a) True

b) False

View Answer

Explanation: The J-K Flip-Flop does not suffer from race condition as the input combination which causes race condition is not present. In the J-K flip-flop, when both inputs are HIGH, the output toggles.

3. In the T Flip-Flop, what does T stand for?

a) Toggle

b) Tuple

c) Tick

d) Time

View Answer

Explanation: In the T Flip-Flop, T stands for Toggle as the Flip-Flop toggles on the active edge of the clock whenever the input T is high. T stands for toggle because when T is HIGH, the output of the circuit toggles.

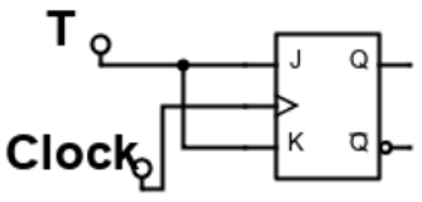

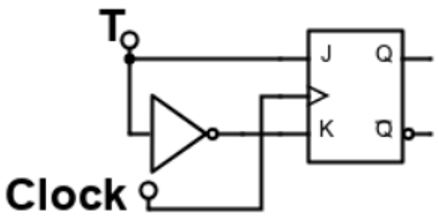

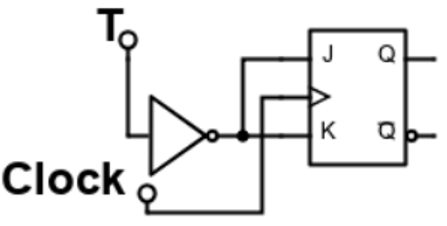

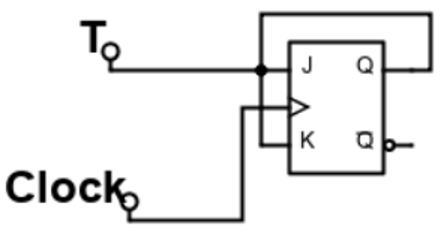

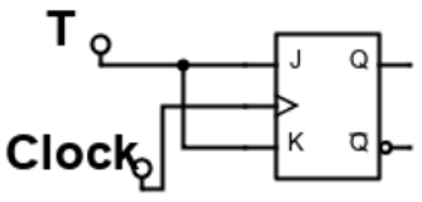

4. How to build T Flip-Flop from a J-K Flip-Flop?

a)

b)

c)

d)

View Answer

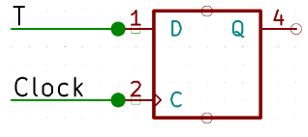

Explanation: The T Flip-Flop is built from the J-K Flip-Flop by connecting J and K inputs together, as shown in the below figure.

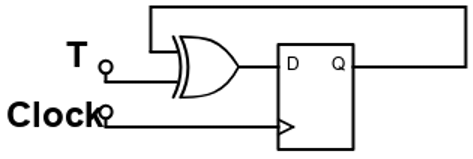

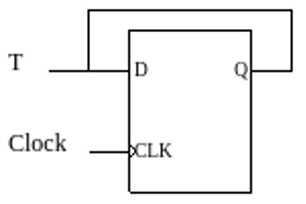

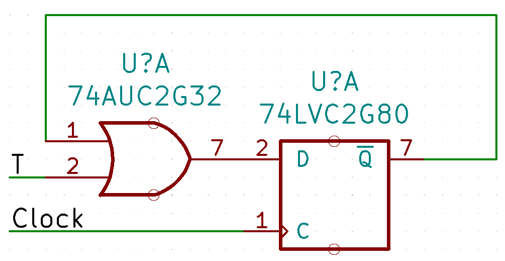

5. How to build a T Flip-Flop from a D Flip-Flop?

a)

b)

c)

d)

View Answer

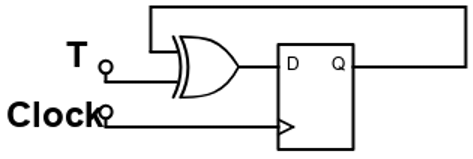

Explanation: The D input is Q ⊕ T. So Q + = Q ⊕ T = T.Q’ + T’.Q, which is the characteristic equation of the T flip-flop. Since the characteristic equation uses an Exclusive OR operation, an XOR gate is used, as shown in the below figure.

6. In the J-K flip-flop, what does J and K stand for?

a) Jack Kilby

b) James Kingston

c) Jones Kane

c) Jill Katie

View Answer

Explanation: In the J-K Flip-Flop, the letter J and K stand for Jack and Kilby respectively. It is named in honor of Jack Kilby, who is considered as the inventor of the Integrated Circuit. Jack Kilby was an employee of Texas Instruments when he invented the Integrated Circuit.

7. If the asynchronous Clear input of a D Flip-Flop is active, then the output Q is set to 0.

a) True

b) False

View Answer

Explanation: The asynchronous Clear input of a D Flip-Flop sets the output Q to 0, when it is active. This operation is asynchronous since it is independent of the clock. The output Q gets set to 0 when the asynchronous clear input becomes active.

8. If the asynchronous Preset input of a D Flip-Flop is active, then the output Q is set to 0.

a) True

b) False

View Answer

Explanation: The asynchronous Preset input of a D Flip-Flop sets the output Q to 1, when it is active. This operation is asynchronous since it is independent of the clock. The output Q gets set to 1 when the asynchronous Preset input becomes active.

9. For a D Flip-Flop with a Clock Enable input, what happens to the output (Q) if the Clock Enable input is inactive?

a) Output toggles

b) Output remains unchanged

c) Output becomes unstable

d) Output becomes 0

View Answer

Explanation: In a D Flip-Flop with a Clock Enable input, the output of the D Flip-Flop does not change if Clock Enable input is inactive. For a D Flip-Flop with a Clock Enable input, the output of the Flip-Flop cannot change unless the clock enable input is active.

10. What is the difference between asynchronous and synchronous sequential circuits?

a) In asynchronous sequential circuits, the state of the circuit can change whenever any input changes. In synchronous sequential circuits, the changes in the state of memory elements are synchronized by a clock signal

b) All synchronous sequential circuits are free from race conditions, but asynchronous sequential circuits are not free from race conditions

c) Synchronous sequential circuits do not have feedback, asynchronous sequential circuits have feedback

d) In synchronous sequential circuits, the state of the circuit can change whenever any input changes. In asynchronous sequential circuits, the changes in the state of memory elements are synchronized by a clock signal

View Answer

Explanation: Asynchronous sequential circuits do not have an input clock, and the state of the circuit can change whenever any input changes. An example for an asynchronous sequential circuit is the Set-Reset Latch.

Sanfoundry Global Education & Learning Series – Logic Design.

To practice all areas of Logic Design, here is complete set of 1000+ Multiple Choice Questions and Answers.

If you find a mistake in question / option / answer, kindly take a screenshot and email to [email protected]