This set of Logic Design Multiple Choice Questions & Answers (MCQs) focuses on “Sequential Circuit Design Using CPLDs”.

1. What does a typical CPLD contain?

a) An array of registers and clocks

b) A combination of multiplexers and decoders

c) A number of macrocells those are grouped into functional blocks

d) A number of interconnected logic gates

View Answer

Explanation: CPLD means Complex Programmable Logic Devices. This has a complexity between PLAs and FPGAs. CPLDs are Complex Program Logic Devices those contain several macrocells grouped into a number of blocks.

2. What is the maximum number of functional blocks available in the Xilinx CoolRunner II CPLD package?

a) 64

b) 256

c) 32

d) 16

View Answer

Explanation: CPLD means Complex Programmable Logic Devices. This has a complexity between PLAs and FPGAs. CPLD family is available in sizes from 2 to 32 functional blocks. Hence the right answer is 32.

3. How many equivalent of AND gates are contained inside of each PLA of the Xilinx CoolRunner II CPLD?

a) 60

b) 56

c) 50

d) 66

View Answer

Explanation: CPLD stands for Complex Programmable Logic Device. It stands between a complexity level of PLAs and FPGAs. The Xilinx CoolRunner II CPLD uses a PLA in each functional block. Each functional block contains equivalent of 56 AND gates.

4. How many inputs does each functional block have from the AIM in the Xilinx CoolRunner II CPLD?

a) 16

b) 40

c) 20

d) 30

View Answer

Explanation: CPLD stands for Complex Programmable Logic Device. It stands between a complexity level of PLAs and FPGAs. Each functional block has 16 inputs from the AIM (Advanced Interconnection Matrix). Hence the correct answer is 20.

5. What is the full form of CPLD?

a) Combinational Programming Logic Device

b) Combinational Purpose Logic Device

c) Complex Programming Logic device

d) Complex Programmed Logic Device

View Answer

Explanation: Full form of CPLD is Complex Programming Logic device. It is a programmable logic device with complexity between PALs and FPGAs.

6. Which one of the following is a noticeable difference between FPGAs and CPLDs?

a) Presence of an in built clock circuit

b) Presence of non volatile on chip memory

c) FPGA has a simpler circuitry

d) FPGAs used more number of sequential circuit components

View Answer

Explanation: FPGAs are Field Programmable Logic Arrays and CPLDs are Complex Programmable Logic Devices. The main difference between FPGAs and CPLDs is the presence of on-chip non volatile memory of CPLDs. It allows CPLDs to be used for boot loader functions.

7. How many flip-flops are needed in designing a shift register using CPLD?

a) 1

b) 2

c) 3

d) 4

View Answer

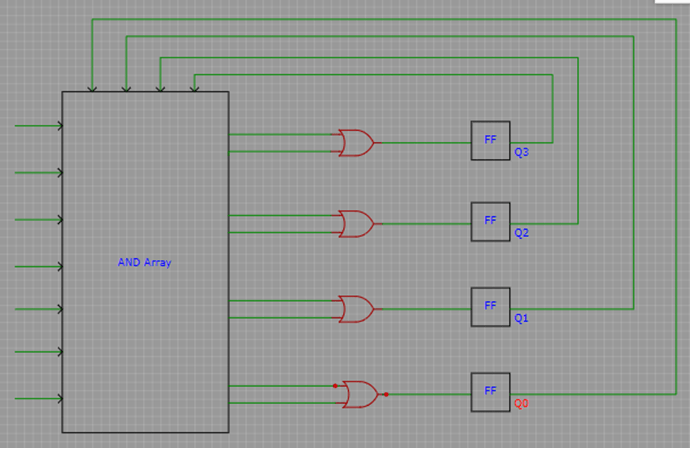

Explanation: Following is the diagram of a shift register designed using CPLD.

It is clear from the diagram that four flip flops are needed.

8. Which one of the following is an essential component of the macrocells of CPLDs?

a) AND gate

b) OR gate

c) NOT gate

d) Flip-flops

View Answer

Explanation: Full form of CPLD is Complex Programming Logic device. It is a programmable logic device with complexity between PALs and FPGAs. Most CPLDs have macrocells with a sum of logic functions and a Flip-flop.

9. Which of the following is used to code in a CPLD designing procedure?

a) VHDL

b) C++

c) Python

d) Assembly

View Answer

Explanation: CPLD means Complex Programmable Logic Devices. This has a complexity between PLAs and FPGAs. CPLDs are Complex Program Logic Devices those contain several macrocells grouped into a number of blocks. The design is first coded in HDL (Verilog or VHDL), once the code is validated (simulated and synthesized).

Sanfoundry Global Education & Learning Series – Logic Design.

To practice all areas of Logic Design, here is complete set of 1000+ Multiple Choice Questions and Answers.

If you find a mistake in question / option / answer, kindly take a screenshot and email to [email protected]