This set of VHDL Multiple Choice Questions & Answers (MCQs) focuses on “Implementing Logic Functions with VHDL – 1”.

1. Which of the following represents the correct order?

a) Given function, optimized function, implementation

b) Optimized function, implementation, given function

c) Implementation, optimized function, given function

d) Given function, implementation, optimized function

View Answer

Explanation: First of all we are given with a logic function that is first optimized before implementing it. The optimization is first done by using a suitable method and then it is implemented in the VHDL.

2. Which of the following will reduce the cost of implementation?

a) Implementing with only one modeling style

b) Implementing with dataflow modeling

c) Optimization

d) Generating Net list first

View Answer

Explanation: Optimization is the technique to get the minimal form for a given logic function. By implementing this minimal function, the cost of implementation is reduced significantly.

3. Which of the following is not a method of optimization of logic function?

a) Tabular method

b) By using Boolean laws

c) K-map

d) Rectangular method

View Answer

Explanation: There are various methods available for optimization of logic functions like K-map, Boolean reduction, tabular method and cubical method. There is no such method called rectangular method to optimize the logic function.

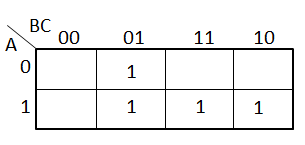

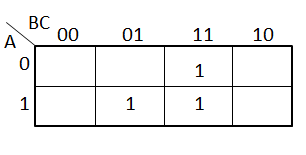

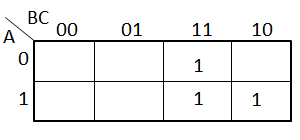

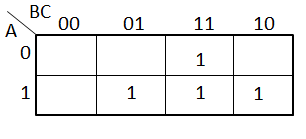

4. Which of the following k-map represents the following given function?

y = AB + AB’C + A’BC

Explanation: In the logic function there are three terms, AB’C representing 101 and A’BC representing 011. Third term is AB which will corresponds to two 1’s which are ABC and ABC’ corresponding to 111 and 110.

5. Which of the following is equivalent to the Boolean expression A + AB?

a) A

b) B

c) AB

d) A + B

View Answer

Explanation: This expression can bide minimized by using simple Boolean laws. In the given expression, let us take A common. This becomes A (1 + B), According to sum laws of Boolean expressions, 1 + B must be equal to 1. So, it becomes A.1 which is equivalent to A.

6. Which of the following assignment statement is not generally used in the implementation of Boolean functions?

a) Concurrent assignment

b) Sequential assignment

c) Conditional assignment

d) Selected assignment

View Answer

Explanation: Generally, these kind of optimized Boolean function doesn’t need any sequential processing and therefore, no sequential assignment is required. All the functions can be implemented with concurrent code only.

7. Which of the following are prime implicants of the following Boolean function?

Y= AB + BC'D’ + BCD'

a) A, B, C, D

b) AB, BC’D’, BCD’

c) AB, BD’

d) AB, CD

View Answer

Explanation: Prime implicants of a function are the terms in the given function without any minimization. In this case the prime implicants are AB, BC’D’, BCD’.

8. How many logical operations are required to implement a Boolean function XY + X?

a) 0

b) 1

c) 2

d) 3

View Answer

Explanation: The given function XY + X is first optimized to reduce the cost of implementation. So, the optimized function will be equal to X. As XY + X = X (Y + 1) = X. To implement this no logical operation is needed. It just needs an assignment statement and no operation.

9. Look the code given below. Which of the following option is implemented by the VHDL code?

ARCHITECTURE my_func OF my_logic IS BEGIN y <= a AND (b XNOR c);

END my_func;

a) B’C’ + BC

b) AB’ + A’B

c) AB’C’

d) ABC + AB’C’

View Answer

Explanation: The given function is a AND (b XNOR c). So, It is Y = A.(B EXNOR C) = AB’C’ + ABC. So, option ABC + AB’C’ is the correct function which is implemented by the code.

10. What is the VHDL code for the logical function AB’C + ABC + BC?

a)

ARCHITECTURE my_logic OF my_logic IS BEGIN y <= (a AND b AND c) AND (b AND c); END ARCHITECTURE;

b)

ARCHITECTURE my_logic OF my_logic IS BEGIN y <= (a AND c) OR (b AND c); END ARCHITECTURE;

c)

ARCHITECTURE my_logic OF my_logic IS BEGIN y <= (a AND c) AND (b OR c); END ARCHITECTURE;

d)

ARCHITECTURE my_logic OF my_logic IS BEGIN y <= (a AND b AND c) OR (b AND c); END ARCHITECTURE;

Explanation: As per the process the function will be implemented after optimization. To optimize the function, AB’C + ABC + BC = AC(B + B’) + BC = AC + BC. So, the correct statement should be A AND C OR B AND C.

Sanfoundry Global Education & Learning Series – VHDL.

To practice all areas of VHDL, here is complete set of 1000+ Multiple Choice Questions and Answers.

If you find a mistake in question / option / answer, kindly take a screenshot and email to [email protected]