This set of Digital Electronic/Circuits Questions & Answers for entrance exams focuses on “Realisation of one Flip-flop using other Flip-flops”.

1. To realise one flip-flop using another flip-flop along with a combinational circuit, known as ____________

a) PREVIOUS state decoder

b) NEXT state decoder

c) MIDDLE state decoder

d) PRESENT state decoder

View Answer

Explanation: To realise one flip-flop using another flip-flop along with a combinational circuit, known as NEXT state decoder which acts as like a flip-flop.

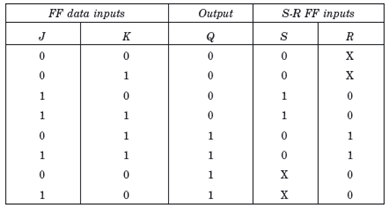

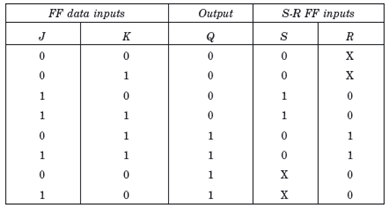

2. For realisation of JK flip-flop from SR flip-flop, the input J and K will be given as ___________

a) External inputs to S and R

b) Internal inputs to S and R

c) External inputs to combinational circuit

d) Internal inputs to combinational circuit

View Answer

Explanation: If a JK Flip Flop is required, the inputs are given to the combinational circuit and the output of the combinational circuit is connected to the inputs of the actual flip flop. So, J and K will be given as external inputs to S and R. As SR flip-flop have invalid state and JK flip-flop don’t.

3. For realisation of JK flip-flop from SR flip-flop, if J=0 & K=0 then the input is ___________

a) S=0, R=0

b) S=0, R=X

c) S=X, R=0

d) S=X, R=X

View Answer

Explanation: If J=0 & K=0, the output will be as: Q(n)=0, Q(n+1)=0 and it is fed into both the AND gates which results as S=0 & R=X(i.e. don’t care).

4. For realisation of JK flip-flop from SR flip-flop, if J=1, K=0 & present state is 0(i.e. Q(n)=0) then excitation input will be ___________

a) S=0, R=1

b) S=X, R=0

c) S=1, R=0

d) S=1, R=1

View Answer

Explanation: If J=1, K=0 & present state is 0(i.e. Q(n)=0) then next state will be 1 which results excitation inputs as S=1 & R=0.

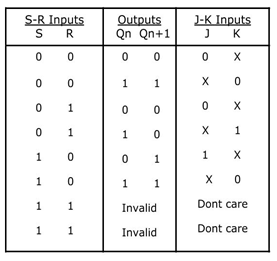

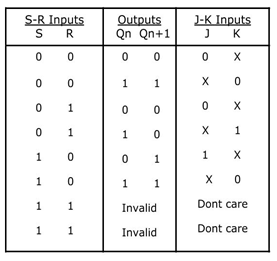

5. For realisation of SR flip-flop from JK flip-flop, the excitation input will be obtained from ___________

a) S and R

b) R input

c) J and K input

d) D input

View Answer

Explanation: It is the reverse process of SR flip-flop to JK flip-flop. So, for realisation of SR flip-flop from JK flip-flop, the excitation input will be obtained from J and K.

6. For realisation of SR flip-flop from JK flip-flop, if S=1, R=0 & present state is 0 then next state will be ___________

a) 1

b) 0

c) Don’t care

d) Toggle

View Answer

Explanation: For JK flip-flop to SR flip-flop, if S=1, R=0 & present state is 0 then next state will be 1 because next stage is complement of present stage.

7. For realisation of SR flip-flop from JK flip-flop, if S=1, R=0 & present state is 0 then the excitation input will be ___________

a) J=1, K=1

b) J=X, K=1

c) J=1, K=X

d) J=0, K=0

View Answer

Explanation: For realisation of SR flip-flop from JK flip-flop, if S=1, R=0 & present state is 0 then the excitation input will be J=1, K=X.

8. The K-map simplification for realisation of SR flip-flop from JK flip-flop is ___________

a) J=1, K=0

b) J=R, K=S

c) J=S, K=R

d) J=0, K=1

View Answer

Explanation: The K-map simplification for realisation of SR flip-flop from JK flip-flop is given by: J=S, K=R.

9. For realisation of D flip-flop from SR flip-flop, the external input is given through ___________

a) S

b) R

c) D

d) Both S and R

View Answer

Explanation: For realisation of D flip-flop from SR flip-flop, S and R are the actual inputs of the flip flop which is connected together via NOT gate and it is called external input as D.

10. For D flip-flop to JK flip-flop, the characteristics equation is given by ___________

a) D=JQ(p)’+Q(p)K’

b) D=JQ(p)’+KQ(p)’

c) D=JQ(p)+Q(p)K’

d) D=J’Q(p)+Q(p)K

View Answer

Explanation: A characteristic equation is needed when a specific gate requires a specific output in order to satisfy the truth table. For D flip-flop to JK flip-flop, the characteristics equation is given by D=JQ(p)’+Q(p)K’.

Sanfoundry Global Education & Learning Series – Digital Circuits.

To practice all areas of Digital Electronic Circuits for entrance exams, here is complete set of 1000+ Multiple Choice Questions and Answers.

If you find a mistake in question / option / answer, kindly take a screenshot and email to [email protected]

- Check Electronics & Communication Engineering Books

- Practice Electrical Engineering MCQs

- Practice Electronics & Communication Engineering MCQs

- Check Digital Electronics Books

- Apply for Electrical Engineering Internship