This set of Digital Electronics/Circuits Multiple Choice Questions & Answers (MCQs) focuses on “D Flip Flop”.

1. In D flip-flop, D stands for _____________

a) Distant

b) Data

c) Desired

d) Delay

View Answer

Explanation: The D of D-flip-flop stands for “data”. It stores the value on the data line.

2. The D flip-flop has _______ input.

a) 1

b) 2

c) 3

d) 4

View Answer

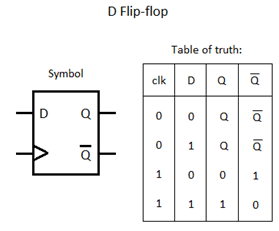

Explanation: The D flip-flop has one input. The D of D-flip-flop stands for “data”. It stores the value on the data line.

3. The D flip-flop has ______ output/outputs.

a) 2

b) 3

c) 4

d) 1

View Answer

Explanation: The D flip-flop has two outputs: Q and Q complement. The D flip-flop has one input. The D of D-flip-flop stands for “data”. It stores the value on the data line.

4. A D flip-flop can be constructed from an ______ flip-flop.

a) S-R

b) J-K

c) T

d) S-K

View Answer

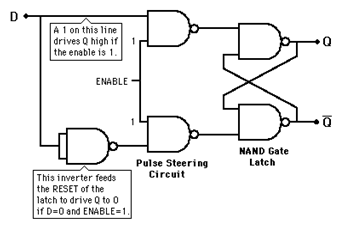

Explanation: A D flip-flop can be constructed from an S-R flip-flop by inserting an inverter between S and R and assigning the symbol D to the S input.

5. In D flip-flop, if clock input is LOW, the D input ___________

a) Has no effect

b) Goes high

c) Goes low

d) Has effect

View Answer

Explanation: In D flip-flop, if clock input is LOW, the D input has no effect, since the set and reset inputs of the NAND flip-flop are kept HIGH.

6. In D flip-flop, if clock input is HIGH & D=1, then output is ___________

a) 0

b) 1

c) Forbidden

d) Toggle

View Answer

Explanation: If clock input is HIGH & D=1, then output is 0. It can be observed from this diagram:

7. Which statement describes the BEST operation of a negative-edge-triggered D flip-flop?

a) The logic level at the D input is transferred to Q on NGT of CLK

b) The Q output is ALWAYS identical to the CLK input if the D input is HIGH

c) The Q output is ALWAYS identical to the D input when CLK = PGT

d) The Q output is ALWAYS identical to the D input

View Answer

Explanation: By the truth table of D flip flop, we can observe that Q always depends on D. Hence, for every negative trigger pulse, the logic at input D is shifted to Output Q.

8. Which of the following is correct for a gated D flip-flop?

a) The output toggles if one of the inputs is held HIGH

b) Only one of the inputs can be HIGH at a time

c) The output complement follows the input when enabled

d) Q output follows the input D when the enable is HIGH

View Answer

Explanation: If clock is high then the D flip-flop operate and we know that input is equals to output in case of D flip-flop. It stores the value on the data line.

9. With regard to a D latch ________

a) The Q output follows the D input when EN is LOW

b) The Q output is opposite the D input when EN is LOW

c) The Q output follows the D input when EN is HIGH

d) The Q output is HIGH regardless of EN’s input state

View Answer

Explanation: Latch is nothing but flip flop which holds the o/p or i/p state. And in D flip-flop output follows the input. It stores the value on the data line.

10. Which of the following is correct for a D latch?

a) The output toggles if one of the inputs is held HIGH

b) Q output follows the input D when the enable is HIGH

c) Only one of the inputs can be HIGH at a time

d) The output complement follows the input when enabled

View Answer

Explanation: If the clock is HIGH then the D flip-flop operates and we know that input equals to output in case of D flip flop. It stores the value on the data line.

11. Which of the following describes the operation of a positive edge-triggered D flip-flop?

a) If both inputs are HIGH, the output will toggle

b) The output will follow the input on the leading edge of the clock

c) When both inputs are LOW, an invalid state exists

d) The input is toggled into the flip-flop on the leading edge of the clock and is passed to the output on the trailing edge of the clock

View Answer

Explanation: Edge-triggered flip-flop means the device will change state during the rising or falling edge of the clock pulse. The main phenomenon of the D flip-flop is that the o/p will follow the i/p when the enable pin is HIGH.

12. A D flip-flop utilizing a PGT clock is in the CLEAR state. Which of the following input actions will cause it to change states?

a) CLK = NGT, D = 0

b) CLK = PGT, D = 0

c) CLOCK NGT, D = 1

d) CLOCK PGT, D = 1

View Answer

Explanation: PGT refers to Positive Going Transition and NGT refers to negative Going Transition. Earlier, the DFF is in a clear state (output is 0). So, if D = 1 then in the next stage output will be 1 and hence the stage will be changed.

13. A positive edge-triggered D flip-flop will store a 1 when ________

a) The D input is HIGH and the clock transitions from HIGH to LOW

b) The D input is HIGH and the clock transitions from LOW to HIGH

c) The D input is HIGH and the clock is LOW

d) The D input is HIGH and the clock is HIGH

View Answer

Explanation: A positive edge-triggered D flip-flop will store a 1 when the D input is HIGH and the clock transitions from LOW to HIGH. While a negative edge-triggered D flip-flop will store a 0 when the D input is HIGH and the clock transitions from HIGH to LOW.

14. Why do the D flip-flops receive its designation or nomenclature as ‘Data Flip-flops’?

a) Due to its capability to receive data from flip-flop

b) Due to its capability to store data in flip-flop

c) Due to its capability to transfer the data into flip-flop

d) Due to erasing the data from the flip-flop

View Answer

Explanation: Due to its capability to transfer the data into flip-flop. D-flip-flops stores the value on the data line.

15. The characteristic equation of D-flip-flop implies that ___________

a) The next state is dependent on previous state

b) The next state is dependent on present state

c) The next state is independent of previous state

d) The next state is independent of present state

View Answer

Explanation: A characteristic equation is needed when a specific gate requires a specific output in order to satisfy the truth table. The characteristic equation of D flip-flop is given by Q(n+1) = D; which indicates that the next state is independent of the present state.

Sanfoundry Global Education & Learning Series – Digital Circuits.

To practice all areas of Digital Circuits, here is complete set of 1000+ Multiple Choice Questions and Answers.

If you find a mistake in question / option / answer, kindly take a screenshot and email to [email protected]